半導体パッケージへのめっき

半導体の製造工程は、ウェハーに回路を形成する「前工程」と、ICチップを切り出して配線を引き、

パッケージングする「後工程」の大きく2つに分けられます。めっきはこの「後工程」の中でも、

パッケージ基板の実装において必要不可欠な技術として使われています。

今回は、半導体パッケージに使われるめっき技術についてご紹介します。

どんな半導体にめっきが使われているのか?

半導体は、スマートフォンやタブレット端末、パソコン、冷蔵庫、洗濯機、カメラ、コピー機、自動車など、私たちの身の回りの様々な製品に搭載され、電圧・電流を制御する役割や記憶や計算をして考える役割を果たしています。もはや私たちの生活は半導体なしでは成り立たないと言っても過言ではないでしょう。

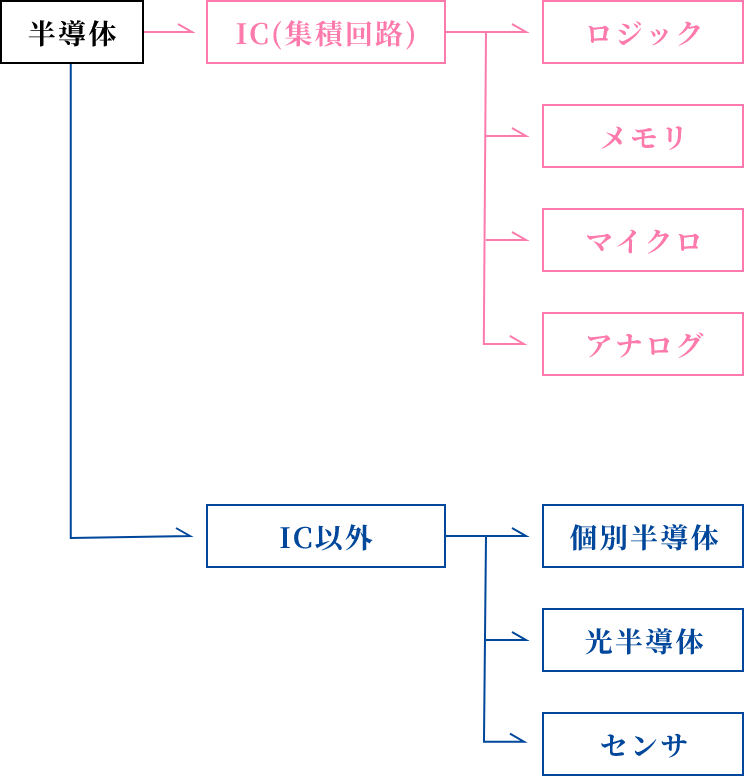

WSTS(世界半導体市場統計)の定義では、半導体は大きくIC(集積回路)とそれ以外に分類されます。ICはさらにロジック、メモリ、マイクロ、アナログの4つに、IC以外は個別半導体(ディスクリート)、光半導体(オプトエレクトロニクス)、センサの3つに分類されます。

このうち、IC(集積回路)でめっきが使われているのは、「ロジック」と「マイクロ」の多次元実装を実現するためのバンプめっき、RDL(再配線めっき)や銅ピラーめっきとなります。

また、ICが搭載されるパッケージ基板の積層配線工程及び最終表面処理にめっきが使われています。「アナログ」にもPMIC(パワーマネジメントIC)が実装される有機基板にめっきが使われています。

IC以外では、「個別半導体」に区分されるパワー半導体のウェハーにめっきが使われています。パワー半導体へのめっきについては、第6話でご紹介します。他にも「光半導体」や「センサ」のウェハーにもめっきが使われています。

パッケージ基板の

どこにめっきが使われているのか?

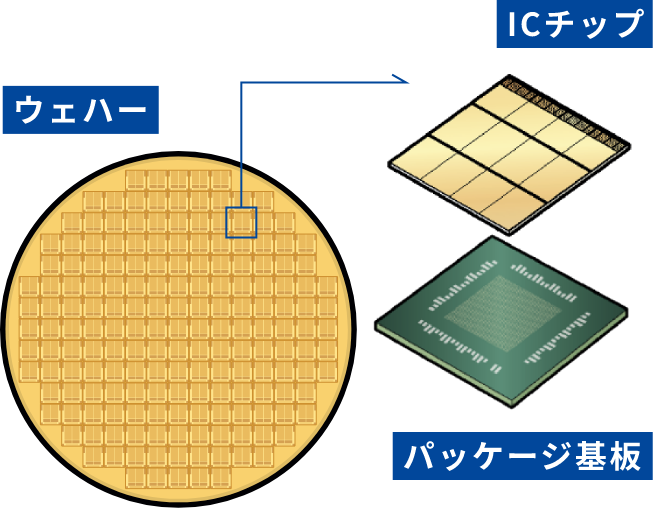

現在、半導体の材料には主にシリコンが使われています。シリコンの単結晶の塊(インゴット)を1 mm程度にスライスして丸い板状にしたものがウェハーで、半導体の「前工程」では、このウェハー上に回路のパターンを作り込みます。

その後の「後工程」では、ウェハーを数 mm~十数 mm角のICチップに切り分けて、パッケージ基板に組み込みます。パッケージ基板には、ICチップを水分やゴミから守る役割やプリント配線板に実装(貼り付け)しやすくする役割があります。

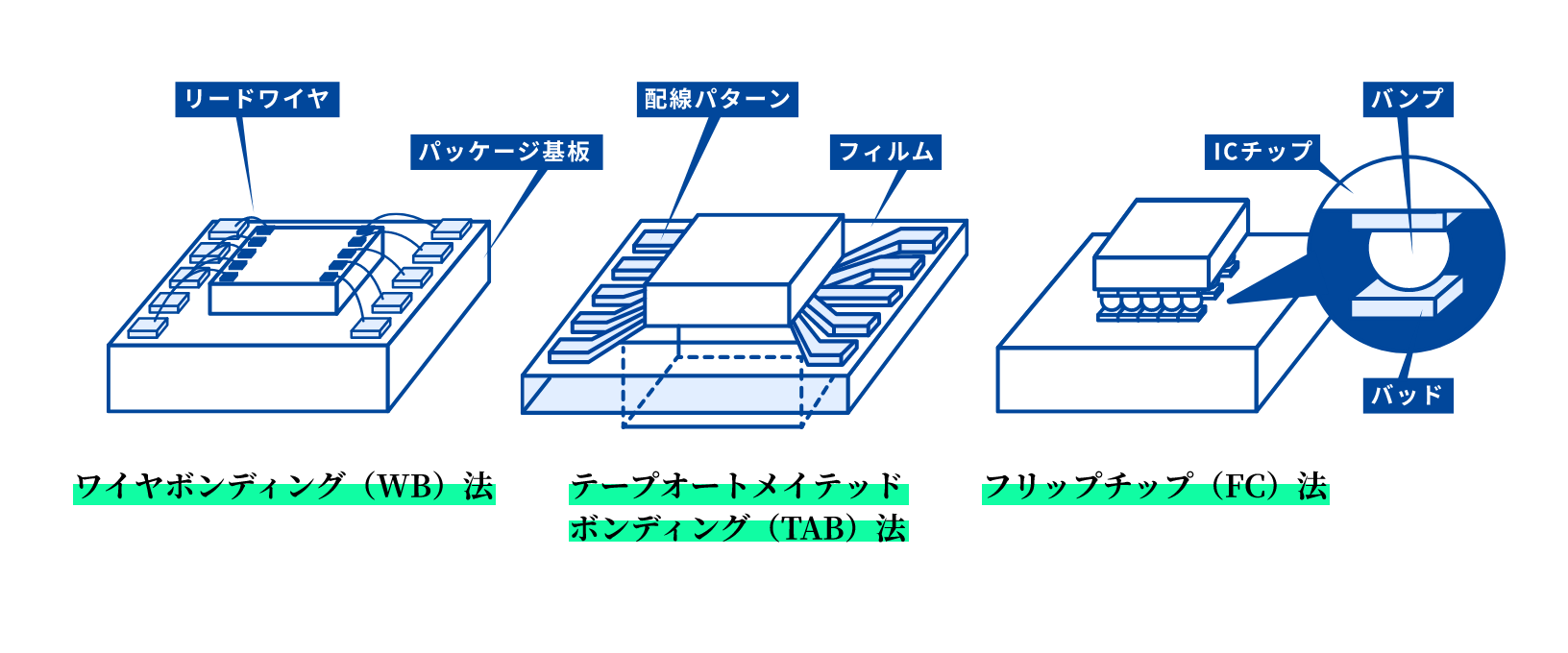

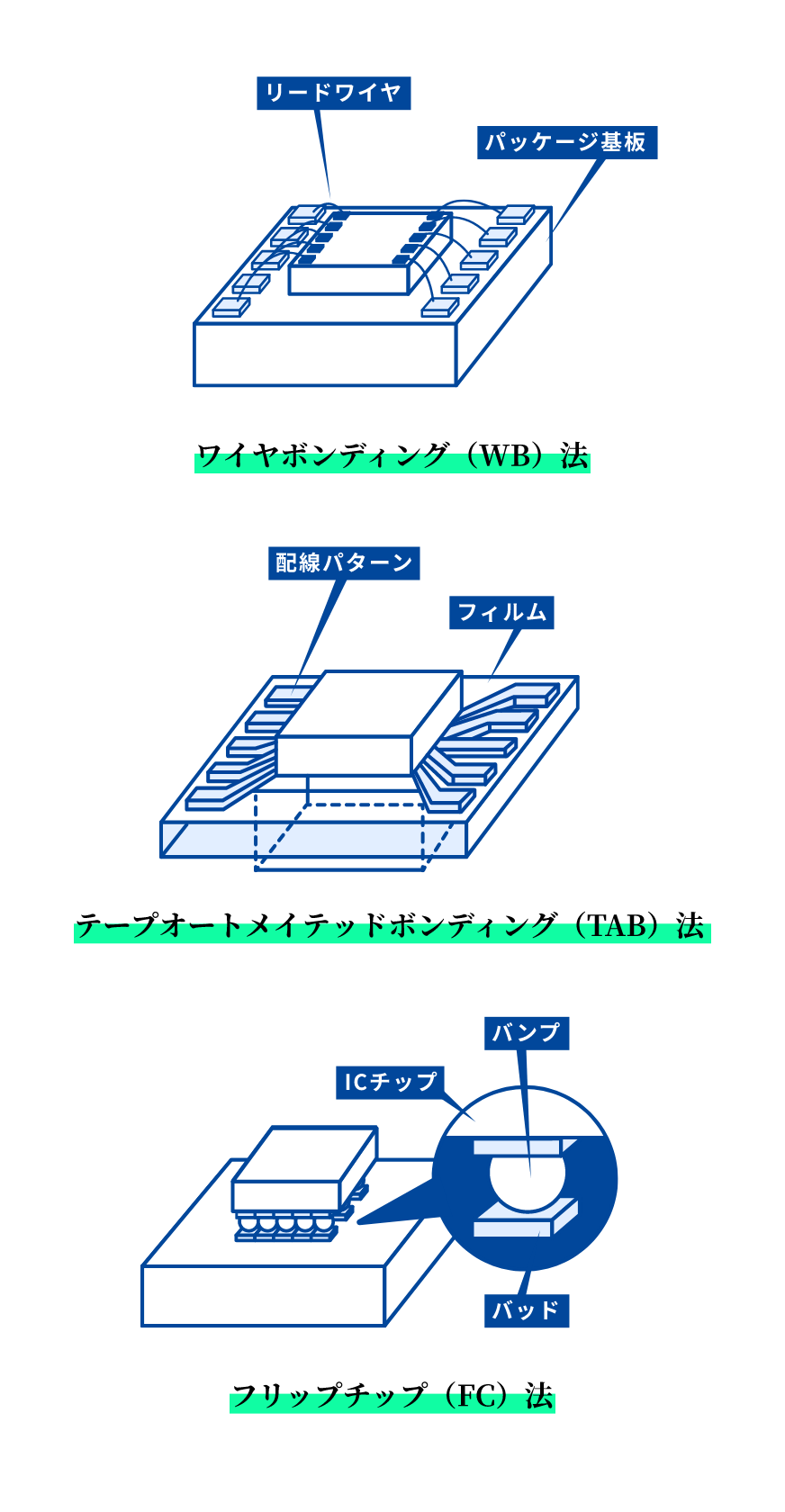

ICチップとパッケージ基板の外部端子を電気的に接続するための方法には、ワイヤボンディング(WB)法、テープオートメイテッドボンディング(TAB)法、フリップチップ(FC)法の3種類があります。

このうちフリップチップ法は、高機能デバイス向けで現在主流の実装方式となっており、フリップチップ法で作られるFC-BGA(Flip Chip-Ball Grid Array)基板は、サーバーやスマートフォン、パソコンなどの幅広い用途で用いられています。

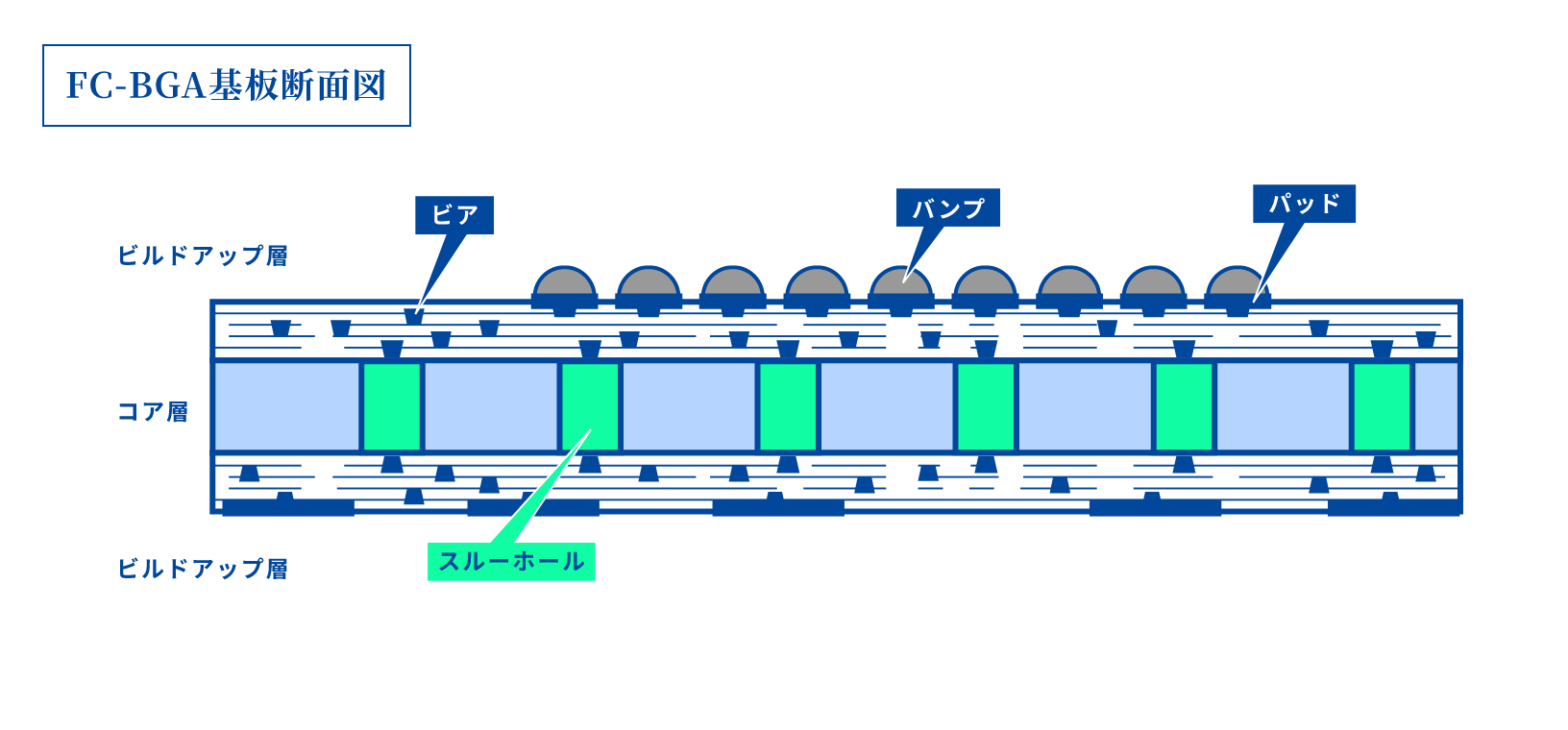

FC-BGA基板のコア層は、銅張積層板(銅箔と樹脂基板を貼り合わせた板)から作られています。このコア層の定められた位置に多数の穴をあけ、両面を電気的に接続するために、穴の内壁に無電解銅めっきを行い、後から必要な厚さの電解銅めっきを行います。この層間を接続する銅めっきのことをスルーホールめっきと言います。

その後、コア層の両面にフィルム状の絶縁材料を重ねて、レーザーで層間を接続する穴(ビア)をあけ、銅めっきで回路を形成します。この工程を何度も繰り返し、ビルドアップ層を形成します。

仕上げにソルダーレジスト(回路パターンを保護する絶縁膜)をコーティングした後、端子に最終表面処理を行います。最終表面処理の目的は、端子の表面にはんだが被覆(濡れ)し、接合し、使用環境で接合の劣化が起こりにくくすることです。最終表面処理には、ENEPIG(無電解ニッケル/パラジウム/金めっき)などを始めとした様々な処理が用途に合わせて使用されています。

今回は、半導体の「後工程」の中でも、主にパッケージ基板の実装に使われるめっき技術についてご紹介しました。半導体デバイスの高機能化に伴い、パッケージ基板の実装においては、線幅やビア径の極小化、導体膜厚の均一化、はんだ接合の信頼性維持などが求められています。そうした要求特性を実現するために、めっきの技術が非常に重要な役割を果たしています。